# **Application Note**

**AN\_299**

# FT800\_FT801\_Internal\_Clock \_Trimming

Version 1.0

Issue Date: 2014-03-04

The FTDI FT800 and FT801 video controllers offer a low cost solution for embedded graphics requirements. In addition to the graphics, touch screen inputs and an audio output provide a complete human machine interface to the outside world.

This application note will provide a programming sequence on how to trim the chip's internal clock for higher accuracy so that applications may run without an external crystal.

Use of FTDI devices in life support and/or safety applications is entirely at the user's risk, and the user agrees to defend, indemnify and hold FTDI harmless from any and all damages, claims, suits or expense resulting from such use.

**Future Technology Devices International Limited (FTDI)**

Unit 1, 2 Seaward Place, Glasgow G41 1HH, United Kingdom Tel.: +44 (0) 141 429 2777 Fax: + 44 (0) 141 429 2758

Web Site: <a href="http://ftdichip.com">http://ftdichip.com</a>

# **Table of Contents**

| 1                                     | Introduction                  |                |                             |   |  |  |  |

|---------------------------------------|-------------------------------|----------------|-----------------------------|---|--|--|--|

| 2                                     |                               | Clock Circuit3 |                             |   |  |  |  |

|                                       |                               |                |                             |   |  |  |  |

| 3                                     |                               | Cloci          | k Trimming Sequence         | 3 |  |  |  |

|                                       | 3.2                           | 1              | Useful Register Description | 4 |  |  |  |

|                                       | 3.2                           | 2              | Trimming Method             | 4 |  |  |  |

|                                       | 3.3                           | 3              | Detailed Sequences          | 4 |  |  |  |

| 4                                     |                               | Cont           | act Information             | 6 |  |  |  |

| Appendix A – References               |                               |                |                             |   |  |  |  |

|                                       | Do                            | cum            | ent References              | 7 |  |  |  |

|                                       | Ac                            | rony           | ms and Abbreviations        | 7 |  |  |  |

| Appendix B – List of Tables & Figures |                               |                |                             |   |  |  |  |

|                                       | Lis                           | st of T        | Tables                      | 8 |  |  |  |

|                                       | List of Figures               |                |                             |   |  |  |  |

| Δr                                    | Appendix C – Revision History |                |                             |   |  |  |  |

|                                       |                               |                |                             |   |  |  |  |

| Re                                    | evis                          | sion F         | History                     | Ĉ |  |  |  |

### 1 Introduction

The FT800/FT801 operates as an SPI or  $I^2C$  peripheral to a main system processor thus providing a low-cost, yet complete, human interface experience by the incorporation of graphics rendering, touch screen sensing and audio capabilities. It is controlled over a low-bandwidth SPI or  $I^2C$  interface allowing practically any microcontroller to be used.

The FT800/FT801 supports both internal clock and external clock operations. The internal clock is a relaxation oscillator which can be trimmed by a register for higher accuracy, so that for many applications external crystal or clock is not required.

#### 2 Clock Circuit

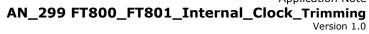

The FT800/FT801 clock circuits include input clock source and PLL. Clock source can be selected between internal relaxation oscillator and 12MHz crystal oscillator. The PLL will multiply the input clock by 4(default) to generate nominal 48MHz system clock, which supply the clock for all internal registers, memories and processors.

The internal relaxation oscillator clock ranges from 4.46MHz to 12.11MHz (untrimmed) and can be trimmed by writing to the trim register (REG\_TRIM). After trimming the clock can reach 12MHz at the tuning accuracy of +/-2.5%. The tuned frequency may vary within +/-3% across operating temperature and voltages.

The FT800/FT801 has 2 output pins which can be used to monitor and calculate the system clock frequency. The PCLK out pin will output a clock with its frequency equals to fsys\_clk / REG\_PCLK (REG\_PCLK programmed to none-zero value). For example, assume the REG\_PCLK is programmed to 5, and the PCLK output frequency is measured at 9.6MHz, in this case the fclk\_sys = 5 \* 9.6MHz = 48MHz.

Alternatively, fclk\_sys can be calculated by measuring the clock frequency on AUDIO\_L pin. The AUDIO\_L pin outputs PWM signal for mono audio signal. The frequency of the PWM signal is fclk\_sys /512. If the measured frequency on AUDIO\_L pin is 93.75kHz, then fclk\_sys = 512 \* 93.75kHz = 48MHz.

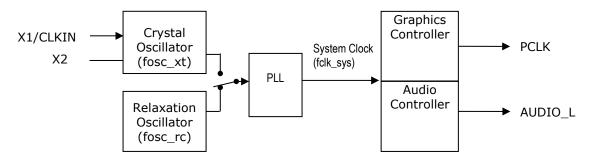

The FT800/FT801 clock circuit is shown in Figure 2-1. For applications using the internal relaxation clock only, the external crystal is not required. In this case the X1/CLKIN pin shall be tied to GND and the X2 pin shall be left unconnected, as shown in Figure 2-2.

Figure 2-1 FT800/FT801 clock circuit

Figure 2-2 internal clock mode pin connection

Document Reference No.: FT\_000987 Clearance No.: FTDI# 373

## **3 Clock Trimming Sequence**

The internal relaxation oscillator frequency is determined by the RC value of the oscillator circuit. The on-chip resistor and capacitor have quite a wide variance across the wafer process. By tuning the effective RC value through registers, it is possible to trim the clock frequency for higher accuracy.

## 3.1 Useful Register Description

There are a number of registers involved in the clock trimming sequences. This section describes in detail the function of these registers.

REG\_TRIM

The trim register REG\_TRIM has 5 valid bits Trim[4:0], which allows total 32 trim settings. Default is 0. When increasing the trim register value the effective RC value of the oscillator decrease, so that the clock frequency increases accordingly.

REG CLOCK

This 32-bit register counts the number of FT800/FT801 main clock cycles since reset. By reading this register, the host MCU can calculate the main clock frequency based on the accurate timer in the MCU.

REG\_FREQUENCY

This 32-bit register stores the value of the current main clock frequency. Software needs to update this register once the clock trimming is completed.

## 3.2 Trimming Method

During power on initialization, software can trim the internal relaxation oscillator clock to the desired value. The target value is 12MHz, so that the main clock will opearate at 48MHz.

After the chip is put into the active mode, the internal clock, PLL, will be running and the system main clock will be available. The REG\_CLOCK will start to count every main clock cycle. By reading the REG\_CLOCK twice in a defined interval (ie. 1us based on MCU clock or timer), the main clock frequency can be calculated. If the measured frequency is lower than the target, increase the value of REG\_TRIM. Repeat this operation until the measured frequency is within +/-3% of the target frequency.

## 3.3 Detailed Sequences

The following steps provide a detailed programming sequence to trim the internal clock.

- After a hardware reset (power on or toggling PD\_N pin), the FT800/FT801 enters STANDBY mode. The internal relaxation oscillator clock is selected as the clock source of the PLL. Both the internal clock and the PLL are turned on, but the main clock to the core logic is turned off.

- 2. Set the chip to ACTIVE mode by doing a dummy read operation through host interface (SPI or I2C).

- 3. Measure the current clock frequency

- a. Read REG\_CLOCK as t0

- b. Delay 1us

- c. Read REG\_CLOCK as t1

- d. Calculate the clock frequency f = (t1-t0) / 1us

- 4. If the measured frequency f is less than 48MHz 3%, increase the REG\_TRIM register by 1

- 5. Repeat steps 3 and 4 until the measured frequency is within 48MHz +/- 3%, or the REG\_TRIM already reaches the maximum value of 31 (which is unlikely since the trimming range is defined to be able to tune the clock to the target)

6. Write the final measured frequency f to REG\_FREQUENCY

Below is the sample C code for internal clock trimming, used by the Gameduinuo 2 application:

```

/**********************************

#define REG_CLOCK

0x102408

uint32_t GDClass::measure_freq(void)

{

unsigned long t0 = GDTR.rd32(REG_CLOCK);

delayMicroseconds(15625);

unsigned long t1 = GDTR.rd32(REG_CLOCK);

return (t1 - t0) << 6;

}

#define REG_TRIM

0x10256C

#define REG_FREQUENCY

0x10240C

#define LOW_FREQ_BOUND 47040000UL

void GDClass::tune(void)

unsigned char i = 0;

uint32_t f;

for (byte i = 0; (i < 31) && ((f = measure\_freq()) < LOW_FREQ_BOUND); i++)

GDTR.wr(REG_TRIM, i);

GDTR.wr32(REG_FREQUENCY, f);

}

```

Since the REG\_TRIM will reset to 0 every time a hardware reset happens, it is required to perform the clock trimming sequence in the reset initialization routine.

Version 1.0

## 4 Contact Information

#### Head Office - Glasgow, UK

Future Technology Devices International Limited Unit 1, 2 Seaward Place, Centurion Business Park Glasgow G41 1HH

United Kingdom

Tel: +44 (0) 141 429 2777 Fax: +44 (0) 141 429 2758

E-mail (Sales) sales1@ftdichip.com

E-mail (Support) support1@ftdichip.com

E-mail (General Enquiries) admin1@ftdichip.com

#### Branch Office - Taipei, Taiwan

Future Technology Devices International Limited

(Taiwan)

2F, No. 516, Sec. 1, NeiHu Road

Taipei 114 Taiwan , R.O.C.

Tel: +886 (0) 2 8791 3570 Fax: +886 (0) 2 8791 3576

E-mail (Sales) <u>tw.sales1@ftdichip.com</u>

E-mail (Sales) <u>tw.sales1@ftdichip.com</u>

E-mail (Support) <u>tw.support1@ftdichip.com</u>

E-mail (General Enquiries) <u>tw.admin1@ftdichip.com</u>

#### Branch Office - Tigard, Oregon, USA

Future Technology Devices International Limited

(USA)

7130 SW Fir Loop Tigard, OR 97223-8160

USA

Tel: +1 (503) 547 0988

Fax: +1 (503) 547 0987

E-Mail (Sales) <u>us.sales@ftdichip.com</u>

E-Mail (Support) <u>us.support@ftdichip.com</u>

E-Mail (General Enquiries) <u>us.admin@ftdichip.com</u>

#### Branch Office - Shanghai, China

Future Technology Devices International Limited (China)

Room 1103, No. 666 West Huaihai Road,

Shanghai, 200052

China

Tel: +86 21 62351596 Fax: +86 21 62351595

#### **Web Site**

http://ftdichip.com

System and equipment manufacturers and designers are responsible to ensure that their systems, and any Future Technology Devices International Ltd (FTDI) devices incorporated in their systems, meet all applicable safety, regulatory and system-level performance requirements. All application-related information in this document (including application descriptions, suggested FTDI devices and other materials) is provided for reference only. While FTDI has taken care to assure it is accurate, this information is subject to customer confirmation, and FTDI disclaims all liability for system designs and for any applications assistance provided by FTDI. Use of FTDI devices in life support and/or safety applications is entirely at the user's risk, and the user agrees to defend, indemnify and hold harmless FTDI from any and all damages, claims, suits or expense resulting from such use. This document is subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Neither the whole nor any part of the information contained in, or the product described in this document, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. Future Technology Devices International Ltd, Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow G41 1HH, United Kingdom. Scotland Registered Company Number: SC136640

version 1.0

# **Appendix A - References**

#### **Document References**

**EVE Product Page**

FT800 Datasheet

FT801 Datasheet

FT800 Programmers Guide

VM800C Datasheet - Credit Card sized development board with FT800

VM800B Datasheet - Bezel-mounted Display with FT800

AN 240 EVE From the Ground Up

AN 259 FT800 Example with 8-bit MCU

## **Acronyms and Abbreviations**

| Terms            | Description                 |

|------------------|-----------------------------|

| GND              | Ground                      |

| EVE              | Embedded Video Engine       |

| I <sup>2</sup> C | Inter-Integrated Circuit    |

| PLL              | Phase Lock Loop             |

| SPI              | Serial Peripheral Interface |

Document Reference No.: FT\_000987 Clearance No.: FTDI# 373

# **Appendix B – List of Tables & Figures**

## **List of Tables**

# **List of Figures**

| Figure 2-1 FT800/FT801 clock circuit          | 3 |

|-----------------------------------------------|---|

| Figure 2-2 internal clock mode pin connection | 3 |

Version 1.0

Document Reference No.: FT\_000987 Clearance No.: FTDI# 373

# **Appendix C - Revision History**

Document Title: AN\_299 FT800\_FT801\_Internal\_Clock\_Trimming

Document Reference No.: FT\_000987

Clearance No.: FTDI# 373

Product Page: <a href="http://www.ftdichip.com/EVE.htm">http://www.ftdichip.com/EVE.htm</a>

Document Feedback: Send Feedback

| Revision | Changes         | Date       |

|----------|-----------------|------------|

| 1.0      | Initial Release | 2014.03.04 |

|          |                 |            |

|          |                 |            |

|          |                 |            |

|          |                 |            |

|          |                 |            |